Förderjahr 2025 / Stipendium Call #20 / ProjektID: 7710 / Projekt: Hardware Design for Post-Quantum Cryptography and Homomorphic Encryption

This work develops efficient and secure hardware design methodology for post-quantum cryptography and explores hardware support for fully homomorphic encryption.

I am thrilled to kick off the first blog post on Hardware for Post-Quantum Cryptography and Homomorphic Encryption, supported by netidee. This initiative aims to establish the hardware foundations for a secure and privacy-aware future.

Why Post-Quantum Cryptography?

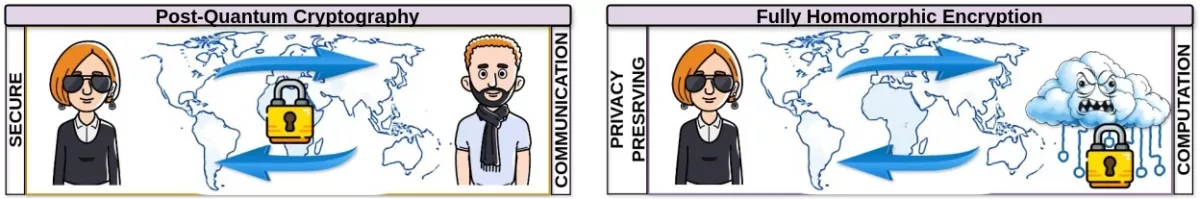

Post-quantum cryptography (PQC) refers to new algorithms that remain secure even against attackers equipped with quantum computers. However, these algorithms, come with high computational demands. Software implementations alone struggle to meet real-world constraints. They can be slow, energy-intensive, or vulnerable to side-channel attacks. That’s why this work focuses on building dedicated hardware that can make PQC practical, efficient, and secure.

In addition to the PQC acceleration, this work also explores post-quantum secure Fully Homomorphic Encryption (FHE). This technology enables computations to be performed directly on encrypted data, without requiring it to be decrypted.

This could enable:

-

privacy-preserving data analytics,

-

secure cloud computation,

-

sensitive IoT data processing,

-

or training AI models on encrypted datasets.

While Pots-Quantum secure Key Encapsulation Mechanisms and Digital Signature Algorithms allow secure key establishment, FHE focuses on privacy-preserving computation. Both technologies address different, but complementary, aspects of modern digital security.

Why One Size Doesn’t Fit All?

There is no "best" implementation of these algorithms. Different applications impose different constraints based on their use-cases and target platforms. The need for an efficient implementation is constant, but the parameters for judging that efficiency, such as Polynomial Degree. N and modulus size (q), change drastically between PQC, and FHE.

- PQC focuses on low-area and low-latency implementations, often for microcontrollers and lightweight IoT platforms.

- FHE on the other hand, emphasize high throughput and performance, typically targeting datacenter-scale compute, or High performnace ASIC chip designs.

Consequently, each direction requires its own dedicated design exploration, as demonstrated in prior research.

What Comes Next

Over the coming months, the work will dive deeper into several key areas:

-

designing and evaluating hardware architectures for PQC acceleration,

-

analyzing computational bottlenecks in homomorphic encryption and identifying where hardware support can make the biggest difference.

The long-term goal is to establish a hardware design methodology for the next era of cryptography. As cloud services expand, the number of IoT devices grows, and digital infrastructure becomes increasingly interconnected, we need security solutions that can withstand both the rise of quantum computing and the growing demand for data privacy.

___

I’m excited to share the progress of this work and contribute to the netidee community throughout the year!